Semicera 3C-SiC Wafer Substrates offer superior thermal conductivity and high electrical breakdown voltage, ideal for power electronic and high-frequency devices. These substrates are precision-engineered for optimal performance in harsh environments, ensuring reliability and efficiency. Choose Semicera for innovative and advanced solutions.

Semicera 3C-SiC Wafer Substrates are engineered to provide a robust platform for next-generation power electronics and high-frequency devices. With superior thermal properties and electrical characteristics, these substrates are designed to meet the demanding requirements of modern technology.

The 3C-SiC (Cubic Silicon Carbide) structure of Semicera Wafer Substrates offers unique advantages, including higher thermal conductivity and a lower thermal expansion coefficient compared to other semiconductor materials. This makes them an excellent choice for devices operating under extreme temperatures and high-power conditions.

With a high electrical breakdown voltage and superior chemical stability, Semicera 3C-SiC Wafer Substrates ensure long-lasting performance and reliability. These properties are critical for applications such as high-frequency radar, solid-state lighting, and power inverters, where efficiency and durability are paramount.

Semicera’s commitment to quality is reflected in the meticulous manufacturing process of their 3C-SiC Wafer Substrates, ensuring uniformity and consistency across every batch. This precision contributes to the overall performance and longevity of the electronic devices built upon them.

By choosing Semicera 3C-SiC Wafer Substrates, manufacturers gain access to a cutting-edge material that enables the development of smaller, faster, and more efficient electronic components. Semicera continues to support technological innovation by providing reliable solutions that meet the evolving demands of the semiconductor industry.

|

Articles |

Production |

Recherche |

Factice |

|

Paramètres de cristal |

|||

|

Polytype |

4H |

||

|

Erreur d'orientation de la surface |

4±0.15° |

||

|

Paramètres électriques |

|||

|

Dopant |

azote de type N |

||

|

Résistivité |

0,015-0.025ohm · cm |

||

|

Paramètres mécaniques |

|||

|

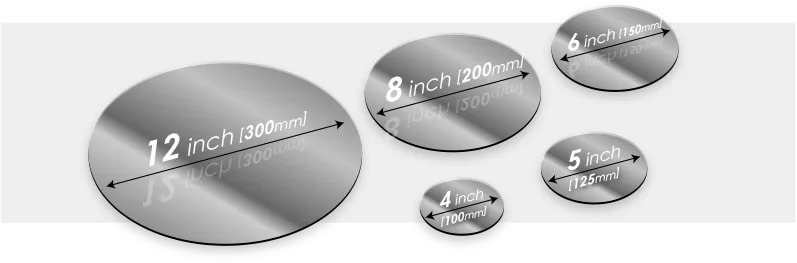

Diamètre |

150,0 ± 0,2 mm |

||

|

Épaisseur |

350 ± 25 µm |

||

|

Orientation plate primaire |

[1-100]±5° |

||

|

Longueur plate primaire |

47,5 ± 1,5 mm |

||

|

Plat secondaire |

Aucun |

||

|

TTV |

≤5 µm |

≤10 µm |

≤15 µm |

|

LTV |

≤3 μm (5 mm * 5 mm) |

≤5 μm (5 mm * 5 mm) |

≤10 μm (5 mm * 5 mm) |

|

Arc |

-15 μm ~ 15μm |

-35 μm ~ 35 μm |

-45 μm ~ 45 μm |

|

Chaîne |

≤35 µm |

≤45 µm |

≤55 µm |

|

Rugosité avant (si-face) (AFM) |

Ra≤0,2 nm (5 μm * 5 μm) |

||

|

Structure |

|||

|

Densité de micro- |

<1 ea / cm2 |

<10 ea / cm2 |

<15 ea / cm2 |

|

Impuretés métalliques |

≤5E10atoms/cm2 |

N / A |

|

|

BPB |

≤1500 ea / cm2 |

≤3000 ea / cm2 |

N / A |

|

TSD |

≤500 ea / cm2 |

≤1000 ea / cm2 |

N / A |

|

Qualité avant |

|||

|

Devant |

Si |

||

|

Finition de surface |

CMP SI-FACE |

||

|

Particules |

≤60ea / plaquette (taille 0,3 μm) |

N / A |

|

|

Rayures |

≤5EA / MM. Longueur cumulative ≤ diamètre |

Longueur cumulatif ≤2 * diamètre |

N / A |

|

PELLE / PEPES ORANGE / TAPPES / COMMENTS / CRESCHES / CONTAMINATION |

Aucun |

N / A |

|

|

Coups de bord / retraits / fracture / plaques hexagonales |

Aucun |

||

|

Zones de polytype |

Aucun |

Zone cumulative≤20% |

Zone cumulative ≤ 30% |

|

Marquage laser avant |

Aucun |

||

|

Qualité du dos |

|||

|

Finition arrière |

CMP C-FACE |

||

|

Rayures |

≤5ea / mm, longueur cumulative≤2 * diamètre |

N / A |

|

|

Défauts arrière (puces de bord / retraits) |

Aucun |

||

|

Rugosité du dos |

Ra≤0,2 nm (5 μm * 5 μm) |

||

|

Marquage laser arrière |

1 mm (du bord supérieur) |

||

|

Bord |

|||

|

Bord |

Chanfreiner |

||

|

Conditionnement |

|||

|

Conditionnement |

Préparé en épi avec un emballage sous vide Emballage de cassette multi-wafer |

||

|

*Remarques: «NA» signifie qu'aucun élément de demande non mentionné ne peut se référer au semi-std. |

|||