850V High Power GaN-on-Si Epi Wafer– Discover the next generation of semiconductor technology with Semicera’s 850V High Power GaN-on-Si Epi Wafer, designed for superior performance and efficiency in high-voltage applications.

Semicera introduces the 850V High Power GaN-on-Si Epi Wafer, a breakthrough in semiconductor innovation. This advanced epi wafer combines the high efficiency of Gallium Nitride (GaN) with the cost-effectiveness of Silicon (Si), creating a powerful solution for high-voltage applications.

Caratteristiche chiave:

• High Voltage Handling: Engineered to support up to 850V, this GaN-on-Si Epi Wafer is ideal for demanding power electronics, enabling higher efficiency and performance.

• Enhanced Power Density: With superior electron mobility and thermal conductivity, GaN technology allows for compact designs and increased power density.

• Cost-Effective Solution: By leveraging silicon as the substrate, this epi wafer offers a cost-effective alternative to traditional GaN wafers, without compromising on quality or performance.

• Wide Application Range: Perfect for use in power converters, RF amplifiers, and other high-power electronic devices, ensuring reliability and durability.

Explore the future of high-voltage technology with Semicera’s 850V High Power GaN-on-Si Epi Wafer. Designed for cutting-edge applications, this product ensures your electronic devices operate with maximum efficiency and reliability. Choose Semicera for your next-generation semiconductor needs.

|

Elementi |

Produzione |

Ricerca |

Manichino |

|

Parametri cristallini |

|||

|

Politipo |

4H |

||

|

Errore di orientamento della superficie |

4±0.15° |

||

|

Parametri elettrici |

|||

|

Drogante |

azoto di tipo n |

||

|

Resistività |

0,015-0,025ohm · cm |

||

|

Parametri meccanici |

|||

|

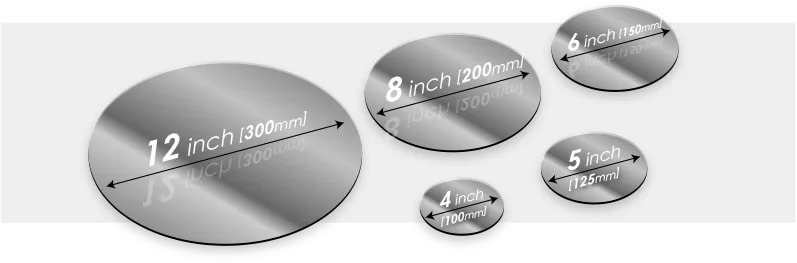

Diametro |

150,0 ± 0,2 mm |

||

|

Spessore |

350 ± 25 µm |

||

|

Orientamento piatto primario |

[1-100]±5° |

||

|

Lunghezza piatta primaria |

47,5 ± 1,5 mm |

||

|

Piatto secondario |

Nessuno |

||

|

TTV |

≤5 µm |

≤10 µm |

≤15 µm |

|

LTV |

≤3 μm (5mm*5mm) |

≤5 μm (5 mm*5 mm) |

≤10 μm (5 mm*5 mm) |

|

Arco |

-15μm ~ 15μm |

-35μm ~ 35 μm |

-45μm ~ 45μm |

|

Ordito |

≤35 µm |

≤45 µm |

≤55 µm |

|

Front (Si-Face) Rughess (AFM) |

RA≤0,2 nm (5μm*5μm) |

||

|

Struttura |

|||

|

Densità di micrivipe |

<1 ea/cm2 |

<10 ea/cm2 |

<15 ea/cm2 |

|

Impurità dei metalli |

≤5E10atoms/cm2 |

N / A |

|

|

BPD |

≤1500 ea/cm2 |

≤3000 ea/cm2 |

N / A |

|

TSD |

≤500 ea/cm2 |

≤1000 ea/cm2 |

N / A |

|

Qualità anteriore |

|||

|

Davanti |

Si |

||

|

Finitura superficiale |

Si-Face CMP |

||

|

Particelle |

≤60ea/wafer (dimensione≥0,3μm) |

N / A |

|

|

Graffi |

≤5ea/mm. Lunghezza cumulativa ≤Diameter |

Diametro cumulativo della lunghezza ≤2* |

N / A |

|

Buccia/pozzi/macchie/striature/crepe/contaminazione |

Nessuno |

N / A |

|

|

Bordo chips/riendi/frattura/piastre esadecimale |

Nessuno |

||

|

Aree politepi |

Nessuno |

Area cumulativa≤20% |

Area cumulativa≤30% |

|

Marcatura laser anteriore |

Nessuno |

||

|

Qualità alla schiena |

|||

|

Finitura posteriore |

C-FACE CMP |

||

|

Graffi |

≤5ea/mm, lunghezza cumulativa≤2*diametro |

N / A |

|

|

Difetti posteriori (bordo chip/rientri) |

Nessuno |

||

|

Rugosità posteriore |

RA≤0,2 nm (5μm*5μm) |

||

|

Marcatura laser sul retro |

1 mm (dal bordo superiore) |

||

|

Bordo |

|||

|

Bordo |

Smussare |

||

|

Confezione |

|||

|

Confezione |

Prepasto EPI con imballaggio a vuoto Packaging a cassette multi-wafer |

||

|

*Note : “NA” significa che nessuna richiesta di richiesta non menzionata può fare riferimento a semi-std. |

|||