Semicera’s SOI Wafer (Silicon On Insulator) provides exceptional electrical isolation and performance for advanced semiconductor applications. Engineered for superior thermal and electrical efficiency, these wafers are ideal for high-performance integrated circuits. Choose Semicera for quality and reliability in SOI wafer technology.

Semicera’s SOI Wafer (Silicon On Insulator) is designed to deliver superior electrical isolation and thermal performance. This innovative wafer structure, featuring a silicon layer on an insulating layer, ensures enhanced device performance and reduced power consumption, making it ideal for a variety of high-tech applications.

Our SOI wafers offer exceptional benefits for integrated circuits by minimizing parasitic capacitance and improving device speed and efficiency. This is crucial for modern electronics, where high performance and energy efficiency are essential for both consumer and industrial applications.

Semicera employs advanced manufacturing techniques to produce SOI wafers with consistent quality and reliability. These wafers provide excellent thermal insulation, making them suitable for use in environments where heat dissipation is a concern, such as in high-density electronic devices and power management systems.

The use of SOI wafers in semiconductor fabrication allows for the development of smaller, faster, and more reliable chips. Semicera’s commitment to precision engineering ensures that our SOI wafers meet the high standards required for cutting-edge technologies in fields like telecommunications, automotive, and consumer electronics.

Choosing Semicera’s SOI Wafer means investing in a product that supports the advancement of electronic and microelectronic technologies. Our wafers are designed to provide enhanced performance and durability, contributing to the success of your high-tech projects and ensuring that you stay at the forefront of innovation.

|

Elementi |

Produzione |

Ricerca |

Manichino |

|

Parametri cristallini |

|||

|

Politipo |

4H |

||

|

Errore di orientamento della superficie |

4±0.15° |

||

|

Parametri elettrici |

|||

|

Drogante |

azoto di tipo n |

||

|

Resistività |

0,015-0,025ohm · cm |

||

|

Parametri meccanici |

|||

|

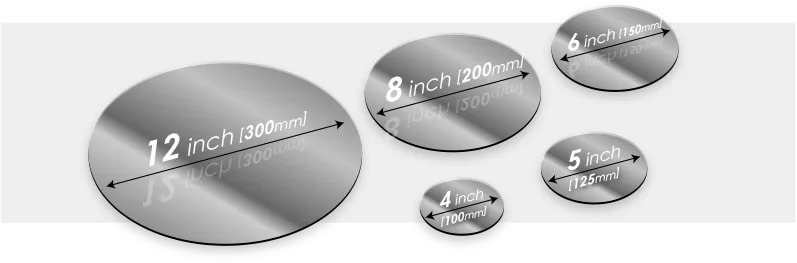

Diametro |

150,0 ± 0,2 mm |

||

|

Spessore |

350 ± 25 µm |

||

|

Orientamento piatto primario |

[1-100]±5° |

||

|

Lunghezza piatta primaria |

47,5 ± 1,5 mm |

||

|

Piatto secondario |

Nessuno |

||

|

TTV |

≤5 µm |

≤10 µm |

≤15 µm |

|

LTV |

≤3 μm (5mm*5mm) |

≤5 μm (5 mm*5 mm) |

≤10 μm (5 mm*5 mm) |

|

Arco |

-15μm ~ 15μm |

-35μm ~ 35 μm |

-45μm ~ 45μm |

|

Ordito |

≤35 µm |

≤45 µm |

≤55 µm |

|

Front (Si-Face) Rughess (AFM) |

RA≤0,2 nm (5μm*5μm) |

||

|

Struttura |

|||

|

Densità di micrivipe |

<1 ea/cm2 |

<10 ea/cm2 |

<15 ea/cm2 |

|

Impurità dei metalli |

≤5E10atoms/cm2 |

N / A |

|

|

BPD |

≤1500 ea/cm2 |

≤3000 ea/cm2 |

N / A |

|

TSD |

≤500 ea/cm2 |

≤1000 ea/cm2 |

N / A |

|

Qualità anteriore |

|||

|

Davanti |

Si |

||

|

Finitura superficiale |

Si-Face CMP |

||

|

Particelle |

≤60ea/wafer (dimensione≥0,3μm) |

N / A |

|

|

Graffi |

≤5ea/mm. Lunghezza cumulativa ≤Diameter |

Diametro cumulativo della lunghezza ≤2* |

N / A |

|

Buccia/pozzi/macchie/striature/crepe/contaminazione |

Nessuno |

N / A |

|

|

Bordo chips/riendi/frattura/piastre esadecimale |

Nessuno |

||

|

Aree politepi |

Nessuno |

Area cumulativa≤20% |

Area cumulativa≤30% |

|

Marcatura laser anteriore |

Nessuno |

||

|

Qualità alla schiena |

|||

|

Finitura posteriore |

C-FACE CMP |

||

|

Graffi |

≤5ea/mm, lunghezza cumulativa≤2*diametro |

N / A |

|

|

Difetti posteriori (bordo chip/rientri) |

Nessuno |

||

|

Rugosità posteriore |

RA≤0,2 nm (5μm*5μm) |

||

|

Marcatura laser sul retro |

1 mm (dal bordo superiore) |

||

|

Bordo |

|||

|

Bordo |

Smussare |

||

|

Confezione |

|||

|

Confezione |

Prepasto EPI con imballaggio a vuoto Packaging a cassette multi-wafer |

||

|

*Note : “NA” significa che nessuna richiesta di richiesta non menzionata può fare riferimento a semi-std. |

|||