Semicera’s P-type SiC Substrate Wafer is engineered for superior electronic and optoelectronic applications. These wafers provide exceptional conductivity and thermal stability, making them ideal for high-performance devices. With Semicera, expect precision and reliability in your P-type SiC substrate wafers.

Semicera’s P-type SiC Substrate Wafer is a key component for developing advanced electronic and optoelectronic devices. These wafers are specifically designed to provide enhanced performance in high-power and high-temperature environments, supporting the growing demand for efficient and durable components.

The P-type doping in our SiC wafers ensures improved electrical conductivity and charge carrier mobility. This makes them particularly suitable for applications in power electronics, LEDs, and photovoltaic cells, where low power loss and high efficiency are critical.

Manufactured with the highest standards of precision and quality, Semicera’s P-type SiC wafers offer excellent surface uniformity and minimal defect rates. These characteristics are vital for industries where consistency and reliability are essential, such as aerospace, automotive, and renewable energy sectors.

Semicera’s commitment to innovation and excellence is evident in our P-type SiC Substrate Wafer. By integrating these wafers into your production process, you ensure that your devices benefit from the exceptional thermal and electrical properties of SiC, enabling them to operate effectively under challenging conditions.

Investing in Semicera’s P-type SiC Substrate Wafer means choosing a product that combines cutting-edge material science with meticulous engineering. Semicera is dedicated to supporting the next generation of electronic and optoelectronic technologies, providing the essential components needed for your success in the semiconductor industry.

|

アイテム |

生産 |

研究 |

ダミー |

|

クリスタルパラメーター |

|||

|

ポリタイプ |

4H |

||

|

表面向きエラー |

4±0.15° |

||

|

電気パラメーター |

|||

|

ドーパント |

N型窒素 |

||

|

抵抗率 |

0.015-0.025OHM・CM |

||

|

機械的パラメーター |

|||

|

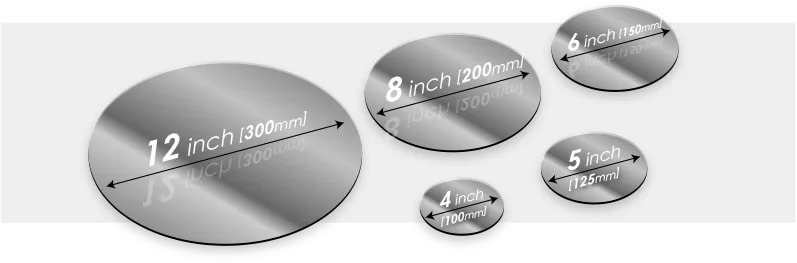

直径 |

150.0±0.2mm |

||

|

厚さ |

350±25 µm |

||

|

一次フラットオリエンテーション |

[1-100]±5° |

||

|

プライマリフラット長 |

47.5±1.5mm |

||

|

二次フラット |

なし |

||

|

TTV |

≤5 µm |

≤10 µm |

≤15 µm |

|

LTV |

≤3μm(5mm*5mm) |

≤5μm(5mm*5mm) |

≤10μm(5mm*5mm) |

|

弓 |

-15μm〜15μm |

-35μm〜35μm |

-45μm〜45μm |

|

ワープ |

≤35 µm |

≤45 µm |

≤55 µm |

|

フロント(si-face)粗さ(AFM) |

RA≤0.2nm(5μm*5μm) |

||

|

構造 |

|||

|

マイクロパイプ密度 |

<1 EA/CM2 |

<10 EA/CM2 |

<15 EA/CM2 |

|

金属の不純物 |

≤5E10atoms/cm2 |

Na |

|

|

BPD |

≤1500 EA/CM2 |

≤3000 EA/CM2 |

Na |

|

TSD |

≤500 EA/CM2 |

≤1000 EA/CM2 |

Na |

|

フロント品質 |

|||

|

フロント |

si |

||

|

表面仕上げ |

SI-FACE CMP |

||

|

粒子 |

≤60EA/ウェーハ(サイズ以上0.3μm) |

Na |

|

|

傷 |

≤5EA/mm。累積長さ≤diameter |

累積長さ2*直径 |

Na |

|

オレンジの皮/ピット/染色/縞/亀裂/汚染 |

なし |

Na |

|

|

エッジチップ/インデント/骨折/ヘックスプレート |

なし |

||

|

ポリタイプの領域 |

なし |

累積面積≤20% |

累積面積以下30% |

|

フロントレーザーマーキング |

なし |

||

|

バック品質 |

|||

|

バックフィニッシュ |

C-Face CMP |

||

|

傷 |

≤5EA/mm、累積長さ2*直径 |

Na |

|

|

バック欠陥(エッジチップ/インデント) |

なし |

||

|

背中の粗さ |

RA≤0.2nm(5μm*5μm) |

||

|

バックレーザーマーキング |

1 mm(上端から) |

||

|

角 |

|||

|

角 |

面取り |

||

|

パッケージング |

|||

|

パッケージング |

真空パッケージングを使用したEPIの準備 マルチワーファーカセットパッケージ |

||

|

*注:「NA」とは、言及されていないリクエスト項目がSemi-STDを参照することはできないことを意味します。 |

|||