Semiceras 4-Zoll-Hochreinheit Semi-INS (HPSI) sic-doppelte polierte Wafer-Substrate sind für überlegene elektronische Leistung präzisionsgestützt. Diese Wafer bieten eine hervorragende thermische Leitfähigkeit und elektrische Isolierung, ideal für fortschrittliche Halbleiteranwendungen. Vertrauens -Semizera für beispiellose Qualität und Innovation in der Wafertechnologie.

Semiceras 4-Zoll-Hochreinheit Semi-Insidat (HPSI) sic-doppelte polierte Wafer-Substrate werden so gestaltet, dass sie den anspruchsvollen Anforderungen der Halbleiterindustrie gerecht werden. Diese Substrate sind mit außergewöhnlicher Flachheit und Reinheit konzipiert und bieten eine optimale Plattform für hochmoderne elektronische Geräte.

Diese HPSI-Wafer zeichnen sich durch ihre überlegenen thermischen Leitfähigkeit und elektrischen Isolationseigenschaften aus, was sie zu einer ausgezeichneten Wahl für hochfrequente und hohe Leistungsanwendungen macht. Der doppelte Polierprozess sorgt für eine minimale Oberflächenrauheit, was für die Verbesserung der Geräteleistung und der Langlebigkeit von entscheidender Bedeutung ist.

Die hohe Reinheit der SIC -Wafer von Semicera minimiert Defekte und Verunreinigungen, was zu höheren Renditen und der Zuverlässigkeit der Geräte führt. Diese Substrate eignen sich für eine Vielzahl von Anwendungen, einschließlich Mikrowellengeräten, Leistungselektronik und LED -Technologien, bei denen Präzision und Haltbarkeit unerlässlich sind.

Mit dem Fokus auf Innovation und Qualität nutzt Semizera fortschrittliche Fertigungstechniken, um Wafer zu erstellen, die den strengen Anforderungen der modernen Elektronik entsprechen. Das doppelseitige Polieren verbessert nicht nur die mechanische Stärke, sondern erleichtert auch eine bessere Integration in andere Halbleitermaterialien.

Durch die Auswahl von Semiceras 4-Zoll-HPSI-HPSI-doppelten polierten Wafer-Substraten können die Hersteller die Vorteile eines verbesserten thermischen Managements und der elektrischen Isolierung nutzen und den Weg für die Entwicklung effizientere und leistungsstarke elektronische Geräte ebnen. Semizera führt die Branche weiterhin mit ihrem Engagement für Qualität und technologischen Fortschritt.

|

Artikel |

Produktion |

Forschung |

Dummy |

|

Kristallparameter |

|||

|

Polytype |

4H |

||

|

Oberflächenorientierungsfehler |

4±0.15° |

||

|

Elektrische Parameter |

|||

|

Dopant |

Stickstoff vom Typ N |

||

|

Widerstand |

0,015-0.025OHM · cm |

||

|

Mechanische Parameter |

|||

|

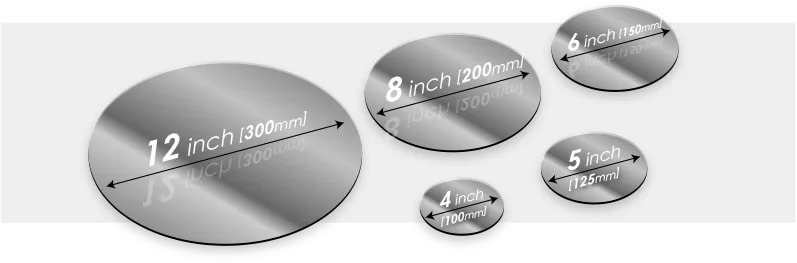

Durchmesser |

150,0 ± 0,2 mm |

||

|

Dicke |

350 ± 25 µm |

||

|

Primäre flache Orientierung |

[1-100]±5° |

||

|

Primäre flache Länge |

47,5 ± 1,5 mm |

||

|

Sekundäre flache |

Keiner |

||

|

Ttv |

≤5 µm |

≤10 µm |

≤15 µm |

|

LTV |

≤3 μm (5 mm*5 mm) |

≤5 μm (5 mm*5 mm) |

≤10 μm (5 mm*5 mm) |

|

Bogen |

-15 μm ~ 15 μm |

-35 μm ~ 35 μm |

-45 μm ~ 45 μm |

|

Kette |

≤35 µm |

≤45 µm |

≤55 µm |

|

Front (Si-Face) Rauheit (AFM) |

Ra ≤ 0,2 nm (5 & mgr; m*5 μm) |

||

|

Struktur |

|||

|

Mikropipe -Dichte |

<1 EA/CM2 |

<10 EA/CM2 |

<15 EA/CM2 |

|

Metallverunreinigungen |

≤5E10atoms/cm2 |

N / A |

|

|

BPD |

≤1500 EA/CM2 |

≤3000 EA/CM2 |

N / A |

|

TSD |

≤500 EA/CM2 |

≤1000 EA/CM2 |

N / A |

|

Frontqualität |

|||

|

Front |

Si |

||

|

Oberflächenbeschaffung |

Si-Face CMP |

||

|

Partikel |

≤60ea/Wafer (Größe ≥ 0,3 μm) |

N / A |

|

|

Kratzer |

≤5ea/mm. Kumulative Länge ≤ Diameter |

Kumulative Länge ≤ 2*Durchmesser |

N / A |

|

Orangenschale/Pits/Flecken/Streifen/Risse/Kontamination |

Keiner |

N / A |

|

|

Kantenchips/Eingeweide/Fraktur-/Sechskantplatten |

Keiner |

||

|

Polytyperbereiche |

Keiner |

Kumulative Fläche ≤ 2010TP3T |

Kumulative Fläche ≤ 30% |

|

Frontlasermarkierung |

Keiner |

||

|

Rückenqualität |

|||

|

Rückbeschluss |

C-Face CMP |

||

|

Kratzer |

≤5ea/mm, kumulative Länge ≤ 2*Durchmesser |

N / A |

|

|

Rückenfehler (Kantenchips/Eingebiete) |

Keiner |

||

|

Rückenrauheit |

Ra ≤ 0,2 nm (5 & mgr; m*5 μm) |

||

|

Rückmarkierung von Laser |

1 mm (von der Oberkante) |

||

|

Rand |

|||

|

Rand |

Chamfer |

||

|

Packaging |

|||

|

Packaging |

Epi-ready with vacuum packaging Multi-wafer cassette packaging |

||

|

*Notes: “NA” means no request Items not mentioned may refer to SEMI-STD. |

|||