Das SIC-Substrat-Wafer vom SIC-Typ des Semicera ist für überlegene elektronische und optoelektronische Anwendungen konstruiert. Diese Wafer bieten eine außergewöhnliche Leitfähigkeit und thermische Stabilität, wodurch sie ideal für Hochleistungsgeräte sind. Erwarten Sie mit Semizera Präzision und Zuverlässigkeit in Ihrem P-Typ-SIC-Substrat.

Das SIC-Substrat-Wafer vom P-Typ von Semicera ist eine Schlüsselkomponente für die Entwicklung fortschrittlicher elektronischer und optoelektronischer Geräte. Diese Wafer sind speziell entwickelt, um eine verbesserte Leistung in Hochleistungs- und Hochtemperaturumgebungen zu bieten und die wachsende Nachfrage nach effizienten und langlebigen Komponenten zu unterstützen.

Das P-Typ-Doping in unseren SIC-Wafern sorgt für eine verbesserte elektrische Leitfähigkeit und Ladungsträgermobilität. Dies macht sie besonders geeignet für Anwendungen in Leistungselektronik, LEDs und Photovoltaikzellen, bei denen niedriger Stromverlust und hohe Effizienz kritisch sind.

Semiceras P-Typ-Wafer werden mit den höchsten Präzisionsnormen und Qualitätsnormen hergestellt und bieten eine hervorragende Oberflächengleichmäßigkeit und minimale Defektraten. Diese Merkmale sind für Branchen von entscheidender Bedeutung, in denen Konsistenz und Zuverlässigkeit wesentlich sind, wie z. B. Luft- und Raumfahrt-, Automobil- und erneuerbare Energien.

Semiceras Engagement für Innovation und Exzellenz zeigt sich in unserem SIC-Substrat-Wafer vom P-Typ. Durch die Integration dieser Wafer in Ihren Produktionsprozess stellen Sie sicher, dass Ihre Geräte von den außergewöhnlichen thermischen und elektrischen Eigenschaften von SIC profitieren, sodass sie unter schwierigen Bedingungen effektiv arbeiten können.

Das Investieren in das SIC-Substrat-Wafer vom P-Typ des Semizeras bedeutet, ein Produkt auszuwählen, das die modernste Materialwissenschaft mit sorgfältiger Ingenieurwesen kombiniert. Semicera unterstützt die nächste Generation elektronischer und optoelektronischer Technologien und bietet die wesentlichen Komponenten, die für Ihren Erfolg in der Halbleiterindustrie benötigt werden.

|

Artikel |

Produktion |

Forschung |

Dummy |

|

Kristallparameter |

|||

|

Polytype |

4H |

||

|

Oberflächenorientierungsfehler |

4±0.15° |

||

|

Elektrische Parameter |

|||

|

Dopant |

Stickstoff vom Typ N |

||

|

Widerstand |

0,015-0.025OHM · cm |

||

|

Mechanische Parameter |

|||

|

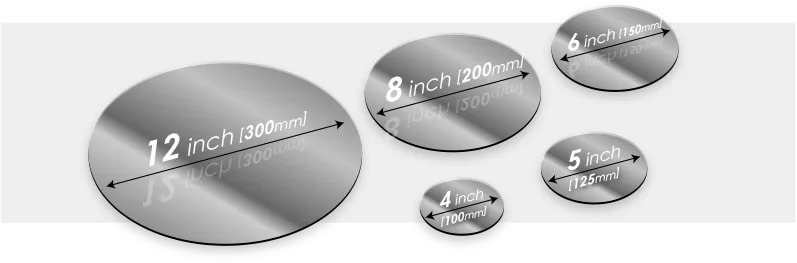

Durchmesser |

150,0 ± 0,2 mm |

||

|

Dicke |

350 ± 25 µm |

||

|

Primäre flache Orientierung |

[1-100]±5° |

||

|

Primäre flache Länge |

47,5 ± 1,5 mm |

||

|

Sekundäre flache |

Keiner |

||

|

Ttv |

≤5 µm |

≤10 µm |

≤15 µm |

|

LTV |

≤3 μm (5 mm*5 mm) |

≤5 μm (5 mm*5 mm) |

≤10 μm (5 mm*5 mm) |

|

Bogen |

-15 μm ~ 15 μm |

-35 μm ~ 35 μm |

-45 μm ~ 45 μm |

|

Kette |

≤35 µm |

≤45 µm |

≤55 µm |

|

Front (Si-Face) Rauheit (AFM) |

Ra ≤ 0,2 nm (5 & mgr; m*5 μm) |

||

|

Struktur |

|||

|

Mikropipe -Dichte |

<1 EA/CM2 |

<10 EA/CM2 |

<15 EA/CM2 |

|

Metallverunreinigungen |

≤5E10atoms/cm2 |

N / A |

|

|

BPD |

≤1500 EA/CM2 |

≤3000 EA/CM2 |

N / A |

|

TSD |

≤500 EA/CM2 |

≤1000 EA/CM2 |

N / A |

|

Frontqualität |

|||

|

Front |

Si |

||

|

Oberflächenbeschaffung |

Si-Face CMP |

||

|

Partikel |

≤60ea/Wafer (Größe ≥ 0,3 μm) |

N / A |

|

|

Kratzer |

≤5ea/mm. Kumulative Länge ≤ Diameter |

Kumulative Länge ≤ 2*Durchmesser |

N / A |

|

Orangenschale/Pits/Flecken/Streifen/Risse/Kontamination |

Keiner |

N / A |

|

|

Kantenchips/Eingeweide/Fraktur-/Sechskantplatten |

Keiner |

||

|

Polytyperbereiche |

Keiner |

Kumulative Fläche ≤ 2010TP3T |

Kumulative Fläche ≤ 30% |

|

Frontlasermarkierung |

Keiner |

||

|

Rückenqualität |

|||

|

Rückbeschluss |

C-Face CMP |

||

|

Kratzer |

≤5ea/mm, kumulative Länge ≤ 2*Durchmesser |

N / A |

|

|

Rückenfehler (Kantenchips/Eingebiete) |

Keiner |

||

|

Rückenrauheit |

Ra ≤ 0,2 nm (5 & mgr; m*5 μm) |

||

|

Rückmarkierung von Laser |

1 mm (von der Oberkante) |

||

|

Rand |

|||

|

Rand |

Chamfer |

||

|

Packaging |

|||

|

Packaging |

Epi-ready with vacuum packaging Multi-wafer cassette packaging |

||

|

*Notes: “NA” means no request Items not mentioned may refer to SEMI-STD. |

|||