Semicera’s P-type SiC Substrate Wafer is engineered for superior electronic and optoelectronic applications. These wafers provide exceptional conductivity and thermal stability, making them ideal for high-performance devices. With Semicera, expect precision and reliability in your P-type SiC substrate wafers.

Semicera’s P-type SiC Substrate Wafer is a key component for developing advanced electronic and optoelectronic devices. These wafers are specifically designed to provide enhanced performance in high-power and high-temperature environments, supporting the growing demand for efficient and durable components.

The P-type doping in our SiC wafers ensures improved electrical conductivity and charge carrier mobility. This makes them particularly suitable for applications in power electronics, LEDs, and photovoltaic cells, where low power loss and high efficiency are critical.

Manufactured with the highest standards of precision and quality, Semicera’s P-type SiC wafers offer excellent surface uniformity and minimal defect rates. These characteristics are vital for industries where consistency and reliability are essential, such as aerospace, automotive, and renewable energy sectors.

Semicera’s commitment to innovation and excellence is evident in our P-type SiC Substrate Wafer. By integrating these wafers into your production process, you ensure that your devices benefit from the exceptional thermal and electrical properties of SiC, enabling them to operate effectively under challenging conditions.

Investing in Semicera’s P-type SiC Substrate Wafer means choosing a product that combines cutting-edge material science with meticulous engineering. Semicera is dedicated to supporting the next generation of electronic and optoelectronic technologies, providing the essential components needed for your success in the semiconductor industry.

|

Unid |

Produção |

Pesquisar |

Fictício |

|

Parâmetros de cristal |

|||

|

Polytype |

4H |

||

|

Erro de orientação da superfície |

4±0.15° |

||

|

Parâmetros elétricos |

|||

|

Dopante |

nitrogênio do tipo n |

||

|

Resistividade |

0,015-0.025OHM · cm |

||

|

Parâmetros mecânicos |

|||

|

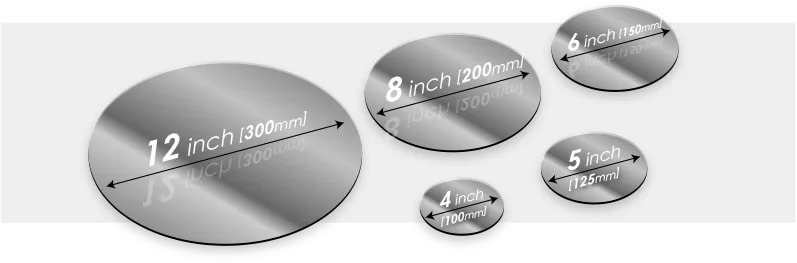

Diâmetro |

150,0 ± 0,2 mm |

||

|

Grossura |

350 ± 25 µm |

||

|

Orientação plana primária |

[1-100]±5° |

||

|

Comprimento plano primário |

47,5 ± 1,5 mm |

||

|

Apartamento secundário |

Nenhum |

||

|

TTV |

≤5 µm |

≤10 µm |

≤15 µm |

|

LTV |

≤3 μm (5mm*5mm) |

≤5 μm (5mm*5mm) |

≤10 μm (5mm*5mm) |

|

Arco |

-15μm ~ 15μm |

-35μm ~ 35μm |

-45μm ~ 45μm |

|

Urdidura |

≤35 µm |

≤45 µm |

≤55 µm |

|

A rugosidade frontal (Si-face) (AFM) |

Ra≤0,2 nm (5μm*5μm) |

||

|

Estrutura |

|||

|

Densidade de micropipe |

<1 ea/cm2 |

<10 ea/cm2 |

<15 ea/cm2 |

|

Impurezas de metal |

≤5E10atoms/cm2 |

N / D |

|

|

Bpd |

≤1500 ea/cm2 |

≤3000 ea/cm2 |

N / D |

|

TSD |

≤500 ea/cm2 |

≤1000 ea/cm2 |

N / D |

|

Qualidade frontal |

|||

|

Frente |

Si |

||

|

Acabamento superficial |

Si-face cmp |

||

|

Partículas |

≤60ea/wafer (size≥0,3μm) |

N / D |

|

|

Arranhões |

≤5ea/mm. Comprimento cumulativo ≤DIAMETER |

Comprimento cumulativo ≤2*diâmetro |

N / D |

|

Casca de laranja/poços/manchas/estrias/rachaduras/contaminação |

Nenhum |

N / D |

|

|

Chips/recuos/fraturas/placas de fratura/placas hexadecimais |

Nenhum |

||

|

Áreas de poliateiro |

Nenhum |

Área cumulativa ≤20% |

Área cumulativa ≤30% |

|

Marcada a laser dianteira |

Nenhum |

||

|

Qualidade de volta |

|||

|

Final traseiro |

CMP C-FACE |

||

|

Arranhões |

≤5ea/mm, comprimento cumulativo≤2*diâmetro |

N / D |

|

|

Defeitos traseiros (chips/recuos de borda) |

Nenhum |

||

|

Rugosidade de volta |

Ra≤0,2 nm (5μm*5μm) |

||

|

Marcação de laser traseiro |

1 mm (da borda superior) |

||

|

Borda |

|||

|

Borda |

Chanfro |

||

|

Embalagem |

|||

|

Embalagem |

Epi pronto com embalagem a vácuo Embalagem de cassetes de várias linhas |

||

|

*Notas : “NA” significa que nenhum item de solicitação não mencionado pode se referir ao Semi-STD. |

|||